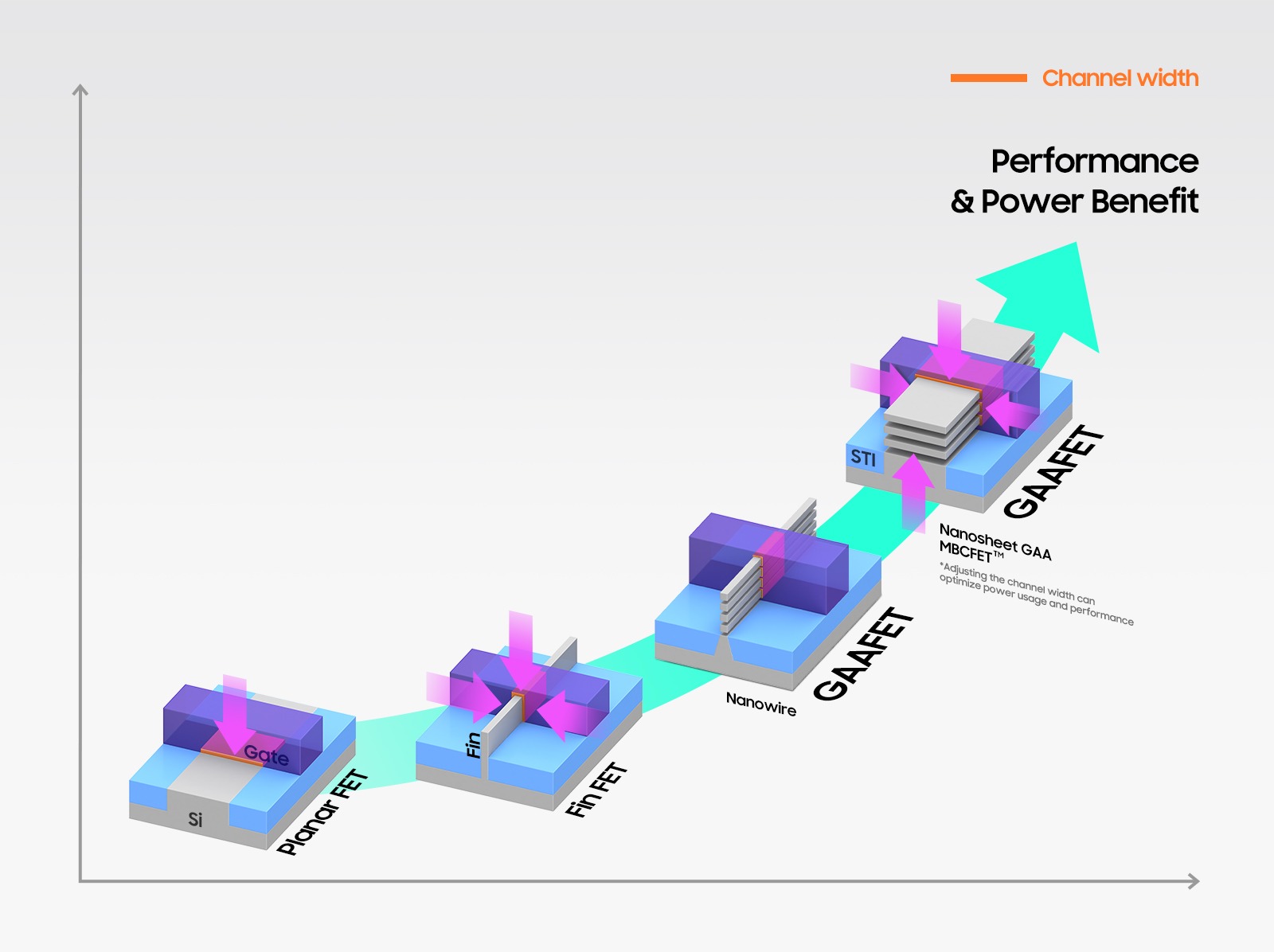

แผนกเซมิคอนดักเตอร์ Samsung Foundry ประกาศว่าได้เริ่มผลิตชิป 3 นาโนเมตรที่โรงงานในเมืองฮวาซอง ต่างจากรุ่นก่อนซึ่งใช้เทคโนโลยี FinFet ปัจจุบันยักษ์ใหญ่เกาหลีใช้สถาปัตยกรรมทรานซิสเตอร์ GAA (Gate-All-Around) ซึ่งช่วยเพิ่มประสิทธิภาพการใช้พลังงานได้อย่างมาก

ชิปขนาด 3 นาโนเมตรที่มีสถาปัตยกรรม GAA ของ MBCFET (Multi-Bridge-Channel) จะได้รับประสิทธิภาพการใช้พลังงานที่สูงขึ้น เหนือสิ่งอื่นใด โดยการลดแรงดันไฟฟ้า ซัมซุงยังใช้ทรานซิสเตอร์นาโนเพลทในชิปเซมิคอนดักเตอร์สำหรับชิปเซ็ตสมาร์ทโฟนประสิทธิภาพสูง

เมื่อเปรียบเทียบกับเทคโนโลยีลวดนาโน แผ่นนาโนที่มีช่องสัญญาณกว้างกว่าช่วยให้มีประสิทธิภาพและประสิทธิผลสูงขึ้น ด้วยการปรับความกว้างของนาโนเพลท ลูกค้าของ Samsung สามารถปรับแต่งประสิทธิภาพและการใช้พลังงานได้ตามความต้องการ

คุณอาจจะสนใจ

เมื่อเทียบกับชิป 5 นาโนเมตร ตามข้อมูลของ Samsung ชิปรุ่นใหม่มีประสิทธิภาพสูงขึ้น 23% ใช้พลังงานน้อยลง 45% และพื้นที่เล็กลง 16% รุ่นที่ 2 ของพวกเขาควรมีประสิทธิภาพดีขึ้น 30% ประสิทธิภาพสูงขึ้น 50% และพื้นที่เล็กลง 35%

“Samsung เติบโตอย่างรวดเร็วในขณะที่เรายังคงแสดงให้เห็นถึงความเป็นผู้นำในการประยุกต์ใช้เทคโนโลยียุคถัดไปในการผลิต เรามุ่งมั่นที่จะสานต่อความเป็นผู้นำนี้ด้วยกระบวนการ 3 นาโนเมตรแรกด้วยสถาปัตยกรรม MBCFETTM เราจะยังคงสร้างสรรค์นวัตกรรมอย่างแข็งขันในการพัฒนาเทคโนโลยีที่มีการแข่งขันและสร้างกระบวนการที่ช่วยเร่งความสำเร็จของความพร้อมทางเทคโนโลยี” Siyoung Choi หัวหน้าฝ่ายธุรกิจเซมิคอนดักเตอร์ของ Samsung กล่าว